集成电路

贡献者: addis

(本文根据 CC-BY-SA 协议转载自原搜狗科学百科对英文维基百科的翻译)

集成电路(integrated circuit)或者单片集成电路(也称为集成电路,芯片,或微芯片)是一组位于一小片(或 “芯片”)半导体材料(通常为硅)上的电子电路。将大量微小的晶体管集成到一个小芯片中使得电路比由分立的电子元件构成的电路小几个数量级、更快、更便宜。集成电路的批量生产能力、可靠性和积木式方法的电路设计使得采用标准化集成电路迅速地取代了使用分立晶体管的设计。集成电路现在几乎被用于所有电子设备,并且已经彻底改变了电子学的世界。计算机、移动电话和其他数字家用电器现在是现代社会结构中不可分割的部分,集成电路的小尺寸和低成本使其成为可能。

20 世纪中期半导体器件制造的技术进步使集成电路变得实用。自从 20 世纪 60 年代问世以来,芯片的尺寸、速度和容量都有了巨大的进步,这是由越来越多的晶体管安装在相同尺寸的芯片上的技术进步所推动的。现代芯片在人类指甲大小的区域内可能有数十亿个晶体管晶体管。这些进展大致跟随摩尔定律,使得今天的计算机芯片拥有上世纪 70 年代早期计算机芯片数百万倍的容量和数千倍的速度。

集成电路相对于分立电路有两个主要优势:成本和性能。成本低是因为芯片及其所有组件通过光刻作为一个单元印刷,而不是一次构造一个晶体管。此外,封装集成电路比分立电路使用的材料少得多。性能之所以高,是因为由于集成电路元件体积小且非常接近,它们的切换速度快,功耗相对较小。集成电路的主要缺点是设计它们和制造所需的光掩模的成本高。这种高初始成本意味着集成电路只有在预计到高产量时才是实用的。

1. 术语

集成电路定义为:[1]

一种电路,其中所有或部分电路元件不可分离地关联并电气互连,因此就结构和商业目的而言,它被认为是不可分割的。

符合该定义的电路可以使用许多不同的技术来构建,包括薄膜晶体管、厚膜技术或混合集成电路。不过,一般情况下集成电路指的是单片集成电路。[2][3]

2. 发明

集成电路的早期发展可以追溯到 1949 年,当时德国工程师沃纳·雅可比[4](西门子)[5]申请了集成电路状半导体放大器的专利[6]示出了公共衬底上的五个晶体管组成的三级放大器。雅可比披露了小巧便宜的助听器作为他专利的典型工业应用。他的专利尚未被报道而立即用于商业用途。

集成电路的概念是由杰弗里·杜默(1909-2002)提出的,一名工作于英国国防部皇家雷达机构的雷达科学家。杜默在公元 1952 年 5 月 7 日华盛顿质量电子元件进展研讨会上向公众提出了这个想法。[7]他公开举办了许多研讨会来宣传他的想法,并在 1956 年试图建造这样一个电路,但没有成功。

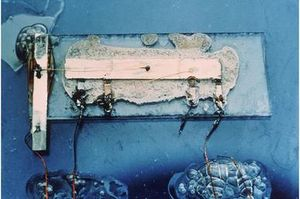

关于集成电路的想法的前身是制造小陶瓷正方形(晶片),每个正方形包含一个小型化的组件。然后,组件可以集成并连线到二维或三维紧凑网格中。这个想法在 1957 年似乎很有希望,是由杰克·基尔比向美国陆军提出的,并导致了短命的小模块计划(类似于 1951 年的 Tinkertoy 项目)。[8][9][10]然而,随着项目势头越来越猛,基尔比提出了一个新的革命性设计: 集成电路。

1958 年 7 月,德州仪器新雇佣的基尔比记录了他关于集成电路的最初想法,并于 1958 年 9 月 12 日成功演示了第一个可工作的集成示例。[11]1959 年 2 月 6 日,在他的专利申请中,[12]Kilby 将他的新设备描述为 “一种半导体材料……其中所有电子电路的组件都是完全集成的。”[13]这项新发明的第一个客户是美国空军。[14]

基尔比赢得了 2000 年的冠物理诺贝尔奖,为了表彰他在集成电路发明中的贡献。[15]2009 年,他的工作被命名为 IEEE 里程碑。[16]

基尔比之后半年,仙童半导体公司的罗伯特·诺伊斯开发了一种新的集成电路,比基尔比的更实用。诺伊斯的设计由硅制成,而基尔比的芯片由锗制成。诺伊斯将以下原理归功于斯普拉格电气的库尔特·利霍韦克 p–n 绝缘结,这也是集成电路背后的关键概念。[17]这种绝缘允许每个晶体管独立工作,尽管它们是同一片硅的一部分。

仙童半导体公司也是第一个拥有自对齐栅极的硅栅集成电路技术的公司,这是所有现代 CMOS 集成电路的基础。这项技术是由意大利物理学家 Federico Faggin 在 1968 年发明的。1970 年,他加入了英特尔,发明了第一个单芯片中央处理单元(CPU)微处理器——英特尔 4004,他因此在 2010 年得到了国家技术和创新奖章。4004 是由 Busicom 的嶋正利和英特尔的泰德·霍夫设计的,但正是 Faggin 在 1970 年改进的设计使其成为现实。[18]

3. 进展

集成电路技术的进步,主要是更小的特征和更大的芯片,使得集成电路中晶体管的数量每两年翻一番,这种趋势被称为摩尔定律。这种增加的容量已被用于降低成本和增加功能。一般来说,随着特征尺寸的缩小,集成电路操作的几乎每个方面都得到改善。每个晶体管的成本和每个晶体管的开关功耗下降,而存储容量和速度上升,这是通过丹纳德标度定义的关系实现的。[19]因为速度、容量和功耗的提高对最终用户来说是显而易见的,所以制造商之间在使用更精细的几何结构方面存在激烈的竞争。多年来,晶体管尺寸已经从 20 世纪 70 年代早期的 10 微米减小到 2017 年的 10 纳米[20]每单位面积的晶体管数量相应地增加了百万倍。截至 2016 年,典型的芯片面积从几平方毫米到大约 600 平方毫米,高达 2500 万晶体管每平方毫米。

国际半导体技术发展蓝图 (ITRS)多年来预测了特征尺寸的预期缩小和相关领域所需的进展。最终的 ITRS 于 2016 年发布,现已被《设备和系统国际路线图》取代。[21]

最初,集成电路严格地说是电子设备。集成电路的成功导致了其他技术的集成,试图获得同样的小尺寸和低成本优势。这些技术包括机械设备、光学和传感器。

- 电荷耦合器件和与其密切相关的有源像素传感器是对光敏感的芯片。在科学、医学和消费者应用中,它们已经在很大程度上取代了照相胶片。现在每年为手机、平板电脑和数码相机等应用生产数十亿台这样的设备。集成电路的这个子领域获得了 2009 年诺贝尔奖。

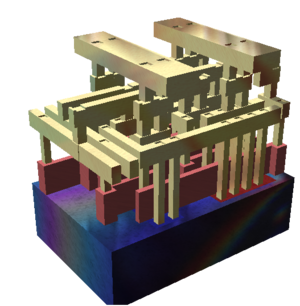

- 由电力驱动的非常小的机械设备可以集成到芯片上,这种技术被称为微电子机械系统。这些设备是在 20 世纪 80 年代后期开发的[22]并且用于各种商业和军事应用。例子包括 DLP 投影仪,喷码机,和被用于汽车的安全气袋上的加速计和微机电陀螺仪.

- 自 21 世纪初以来,将光学功能(光学计算)集成到硅芯片中一直在学术研究和工业上积极进行,使得将光学器件(调制器、检测器、路由)与 CMOS 电子器件相结合的硅基集成光学收发器成功商业化。[23] 集成光学电路也在开发中,使用了新兴的物理领域,即光子学。

- 集成电路也正在为在医疗植入物或其他生物电子设备中的传感器的应用而开发。[24]在这种生物环境中必须应用特殊的密封技术,以避免暴露的半导体材料的腐蚀或生物降解。[25]

截至 2018 年,绝大多数晶体管都是使用平坦的二维平面工艺,在硅芯片一侧的单层中制造的。研究人员已经生产了几种有希望的替代品的原型,例如:

- 堆叠几层晶体管以制造三维集成电路(3DC)的各种方法,例如硅通孔,“单片 3D”,[26]堆叠引线接合,[27]和其他方法。

- 由其他材料制成的晶体管:石墨烯晶体管 s .辉钼矿晶体管,碳纳米管场效应晶体管,氮化镓晶体管,类似晶体管纳米线电子器件,有机晶体管等等。

- 在小硅球的整个表面上制造晶体管。[28][29]

- 对衬底的修改,通常是为了制造用于柔性显示器或其它柔性电子学的柔性晶体管,可能向卷轴式计算机的方向发展。

随着制造越来越小的晶体管变得越来越困难,公司正在使用多晶片模组、三维晶片、3D 与非门、封装在封装上和硅穿孔来提高性能和减小尺寸,而不必减小晶体管的尺寸。[30] [31][32]

4. 设计

设计和开发复杂集成电路的成本相当高,通常高达数千万美元。[33]因此,生产高产量的集成电路产品只有经济意义,因此非经常性工程 (NRE)成本通常分散在数百万个生产单元中。

现代半导体芯片有数十亿个组件,过于复杂,无法手工设计。帮助设计师的软件工具至关重要。电子设计自动化(电子设计自动化),也称为电子计算机辅助设计(适应型),[34]是一类用于设计包括集成电路在内的电子系统的软件工具。这些工具在工程师用来设计和分析整个半导体芯片的设计流程中协同工作。

5. 类型

集成电路可以分为模拟,[35] 数字[36]和混合信号,[37]由同一集成电路上的模拟和数字信号组成。

数字集成电路可以在几平方毫米上包含一个[38]到几十亿[39]个逻辑门、触发器、多路复用器和其他电路。与板级集成相比,这些电路的小尺寸允许高速、低功耗,并降低了制造成本。这些数字集成电路,通常是微处理器、DSP 和微控制器,使用布尔代数来处理 “1” 和 “0” 信号。

最先进的集成电路有微处理器或 “内核”,它可以控制任何电子产品,从个人计算机和蜂窝电话到数字微波炉。数字存储芯片和专用集成电路(ASICs)是对现代信息社会很重要的另外一些集成电路家族的例子。

在 20 世纪 80 年代,可编程逻辑设备被开发出来。这些器件包含的电路的逻辑功能和连接性可以由用户编程,而不是由集成电路制造商固定。这允许单个芯片被编程以实现不同的大规模集成电路类型的功能,例如逻辑门,加法器寄存器。可编程性至少有四种形式——可以仅编程一次,可以使用紫外线擦除然后重新编程的设备,可以使用闪寸(重新)编程的设备,和可编程门阵列 (FPGAs),可随时编程,包括在运行期间。目前的 FPGA(截至 2016 年)可以实现相当于数百万个门的功能,运行频率最高可达 1GHz。[39]

模拟集成电路,如传感器、电源管理电路和运算放大器,通过处理连续信号来工作。它们执行模拟功能,如放大、有源滤波器、解调和混频。模拟集成电路提供专业设计的模拟电路,而不是从头开始设计和构建困难的模拟电路,从而减轻电路设计者的负担。

集成电路也可以将模拟和数字电路结合在单个芯片上来创建功能,如模数转换器和数模转换器。在 20 世纪 90 年代末之前,无线电不能用与微处理器相同的低成本 CMOS 工艺制造。但是自 1998 年以来,已经使用 CMOS 工艺开发了大量无线电芯片。例如英特尔的 DECT 无绳电话,或由 Atheros 和其他公司开发的 802.11 ( 无线网络)芯片。[40]

现代电子元件分销商通常会对现有的各种集成电路进一步细分:

- 数字集成电路进一步细分为逻辑集成电路、存储器芯片、接口集成电路(电平转换器、串行器/解串行器)等。)、电源管理 IC 和可编程器件。

- 模拟集成电路进一步细分为线性集成电路和无线电频率集成电路。

- 混合讯号积体电路进一步细分为数据采集集成电路(包括单仪器模数转换转换器、数模转换器、数字电位计和时钟/定时集成电路)。

6. 制造业

6.1 制造

化学元素的周期表中的半导体被认为是最有可能形成固态真空管的材料。从氧化铜到锗,再到硅,这些材料在 20 世纪 40 年代和 50 年代得到了系统的研究。今天,单晶硅是集成电路的主要衬底,尽管元素周期表中的一些 III-V 化合物如砷化镓用于特殊应用,如发光二极管、激光器、太阳能电池和高速集成电路。人们用了几十年的时间来完善在半导体材料的晶体结构中产生具有最小缺陷的晶体的方法。

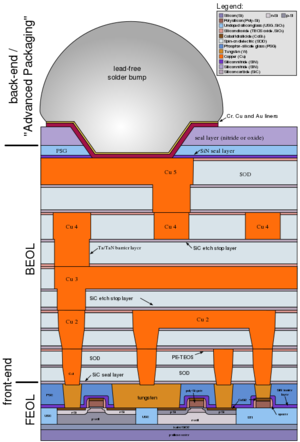

半导体集成电路在平面工艺中制造,包括三个关键工艺步骤 — 光刻,沉积(例如化学汽相淀积),以及蚀刻版画。主要工艺步骤由掺杂和清洗补充。

单晶硅晶片用于大多数应用(对于特殊应用,使用其他半导体,例如砷化镓)。晶片不必完全是硅。光刻法用于标记衬底的不同区域以进行掺杂,或者在其上沉积多晶硅、绝缘体或金属(通常是铝或铜)。掺杂剂是有意引入半导体以调节其电子特性的杂质。掺杂是向半导体材料中添加掺杂剂的过程。

- 集成电路由许多重叠的层组成,每个层由光刻法定义,通常以不同的颜色显示。一些层标记了各种掺杂剂扩散到衬底中的位置(称为扩散层),一些层定义了附加离子注入的位置(注入层),一些层定义了导体(掺杂多晶硅或金属层),一些层定义了导电层之间的连接(过孔或接触层)。所有组件都是由这些层的特定组合构成的。

- 在自对准 CMOS 工艺中,在栅极层(多晶硅或金属)穿过扩散层的任何地方都会形成晶体管。

- 电容结构的形式非常类似于传统的电电容器的平行导电板,根据 “板” 的区域形成,板之间具有绝缘材料。各种尺寸的电容器在集成电路中很常见。

- 不同长度的曲折条纹有时用于形成片上电阻器,尽管大多数逻辑电路不需要任何电阻。电阻结构的长度与宽度之比,结合其薄层电阻率,决定了电阻的大小。

- 更罕见的是,电感结构可以构建为微小的片上线圈,或者由回转器模拟。

因为 CMOS 器件仅在逻辑状态切换的过程中产生电流,所以 CMOS 器件比双极结型晶体管器件消耗更少的电流。

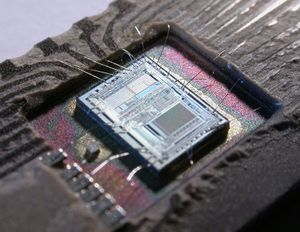

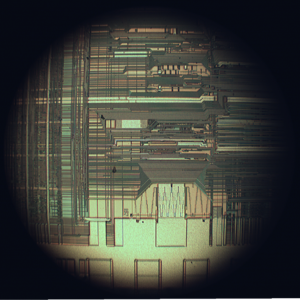

随机存取存储器是最常规类型的集成电路;因此,密度最高的设备是存储器;但是即使是微处理器芯片上也有内存。(参见第一幅图像底部的规则阵列结构。[哪个/哪些?])尽管结构错综复杂——宽度已经缩小了几十年——但这些层仍然比器件宽度薄得多。虽然可见光谱中的光波不能用于 “曝光” 材料,因为它们对于特征尺寸来说太大了。因此,较高频率的光子(通常为紫外线)用于为每一层创建图案。因为每个特征尺寸都很小,电子显微镜是工艺工程师的重要工具,工程师可能正在对制造工艺进行调试。

每个器件在封装之前都要使用自动测试设备(ATE)进行测试,这一过程被称为晶圆测试或晶圆探测。然后将晶片切割成矩形块,每个矩形块称为裸片。然后使用铝(或金)键合线将每个好的裸片到封装中,键合线使用热超声键合[41]到衬垫,通常在模具边缘附近。热声键合最初是由 A. Coucoulas 引入的,它提供了与外部世界形成这些重要电气连接的可靠手段。封装后,器件在晶片探测过程中使用的相同或相似 ATE 上进行最终测试。也可以使用工业 CT 扫描。测试成本可以占低成本产品制造成本的 25% 以上,但在低产量、较大或较高成本的设备上可以忽略不计。

截至 2016 年,一个半导体工厂建设成本可能超过 80 亿美元。[42]由于新产品越来越复杂,半导体工厂的成本会随着时间的推移而上升。这被称为岩石定律。如今,最先进的流程采用了以下技术:

- 晶圆直径高达 300 毫米(比普通的餐盘宽)。

- 截至 2016 年,拥有先进工艺的公司可以生产 14nm 的晶体管,例如英特尔,台积电,三星和格罗方德。[43]

- 铜互连,其中铜布线代替铝用于互连。

- 低介电常数材料 绝缘体。

- 绝缘体上硅 (SOI)。

- IBM 公司使用的应变硅技术,被称为直接应变绝缘体上硅(SSDOI)。

- 多闸极电晶体,例如三栅晶体管,2011 年由英特尔在 22 nm 工艺制程中生产。

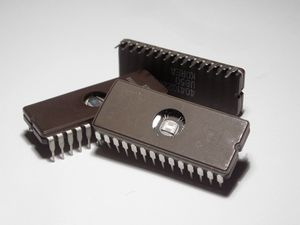

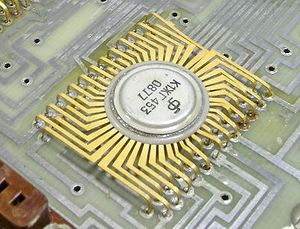

6.2 封装

最早的集成电路是封装在扁平陶瓷片中的,因为其可靠性和体积小,多年来一直被军方使用。商业电路封装迅速转移到双列直插封装(DIP),先是陶瓷,后来是塑料。在 20 世纪 80 年代,超大规模集成电路的引脚数超过了 DIP 封装的实际限制,从而产生了引脚网格阵列(PGA)和 LCC 封装。表面贴装封装出现在 20 世纪 80 年代初,并在 80 年代末开始流行,使用更细的引脚间距,引脚形成鸥翼或 J 形引脚,如小轮廓集成电路(SOIC)包装——一种载体,其占据的面积比同等的 DIP 小 30-50%,通常薄 70%。该封装具有从两个长边突出的 “鸥翼” 引线,引线间距为 0.050 英寸。

在 20 世纪 90 年代末,塑料四方扁平包装(PQFP)和薄型小外形封装(TSOP)封装成为最常见的高引脚数器件,尽管 PGA 封装仍然用于高端微处理器。

球栅阵列(BGA)封装自 20 世纪 70 年代就已存在。倒装球栅阵列与其他封装类型相比,封装允许更高的引脚数,这是在 20 世纪 90 年代发明的。在 FCBGA 封装中,裸片被倒置(翻转)安装,并通过类似于印刷电路板的封装基板而不是通过导线连接到封装球。FCBGA 封装允许输入输出信号(称为区域 I/O)分布在整个芯片上,而不是局限于芯片外围。BGA 器件的优点是不需要专用插座,但在器件故障的情况下更难更换。

从 2004 年开始,英特尔从 PGA 转型为 LGA 和 BGA,最后一个 PGA 于 2014 年发布,用于移动平台。截至 2018 年 AMD 在主流桌面处理器上使用 PGA 封装,[44]移动处理器上使用 BGA 封装,[45]高端台式机和服务器微处理器使用 LGA 封装。[46]

离开裸片的电信号必须穿过将裸片电气连接到封装的材料,穿过封装中的导电迹线(路径),穿过将封装连接到 PCB 上的导电迹线的引线。与传输到同一芯片不同部分的材料和结构相比,这些电信号必经的路径中使用的材料和结构具有非常不同的电气特性。因此,它们需要特殊的设计技术来确保信号不被破坏,并且比限于芯片本身的信号的电气功率大得多。

当多个裸片被放入一个封装中时,得到封装中的系统,缩写为 SiP。多芯片模块(MCM)是通过在通常由陶瓷制成的小衬底上组合多个管芯而产生的。大 MCM 和小 PCB 的区别有时很模糊。

封装的集成电路通常足够大,以包含识别信息。四个常见的部分是制造商的名称或徽标、零件号、零件生产批号和序列号,以及一个四位数日期代码,用于标识芯片的制造时间。极小的表面贴装技术部件通常只带有制造商的查找表中用于查找集成电路特性的数字。

制造日期通常表示为两位数的年份,后跟两位数的周代码,因此带有代码 8341 的零件是在 1983 年的第 41 周制造的,或者大约在 1983 年 10 月制造的。

7. 知识产权

通过拍摄集成电路的每一层并根据获得的照片为其生产准备光掩模来复制芯片的可能性是引入保护布图设计的立法的原因。1984 年的半导体芯片保护法确立了用于生产集成电路的光掩模的知识产权保护。[47]

1989 年在华盛顿哥伦比亚特区举行了一次外交会议,通过了保护集成电路知识产权的华盛顿公约[48](《IPIC 条约》)。

《集成电路知识产权条约》,又称《华盛顿条约》或《IPIC 条约》(1989 年 5 月 26 日在华盛顿签署),目前尚未生效,但已部分纳入《TRIPS 协定》。[49]

许多国家已经通过了保护集成电路布图设计的国家法律,包括日本,[50] EC,[51]英国、澳大利亚和韩国。英国在最初采取版权法完全保护芯片拓扑的立场后,于 1988 年颁布了《版权、设计和专利法》,约为 48,213 年。见罗孚集团汽车公司诉阿姆斯特朗专利公司

美国芯片行业对英国版权方法不足的批评总结在进一步的芯片权利发展中。[52]

澳大利亚通过了 1989 年的电路布局法独特的芯片保护的形式。韩国通过了半导体集成电路布图设计法。

8. 其他发展

未来的发展似乎遵循英特尔和 AMD 多核处理器已经使用的多核多微处理器范例。Rapport 和 IBM 于 2006 年开始推出 256 核微处理器 KC256。就在 2011 年 2 月至 8 月,英特尔推出了一款搭载 80 个内核的 “非商业销售” 芯片原型。每个核心都能够独立于其他核心处理自己的任务。这是对使用现有晶体管技术(参见:热设计功率)即将达到的热速极限的响应。这种设计对芯片编程提出了新的挑战。并行语言比如开源软件 X10 编程语言旨在帮助完成这项任务。[53]

9. 世代

在简单集成电路的早期,该技术的大规模将每个芯片限制在只有几个晶体管,低集成度意味着设计过程相对简单。以今天的标准来看,制造产量也相当低。随着技术的进步,数百万,然后数十亿[54]的晶体管可以放置在一个芯片上,良好的设计需要彻底的规划,产生了电子设计自动化,即 EDA。

| 姓名 | 意义 | 年 | 晶体管的编号[55] | 逻辑门的编号[56] |

| SSI | 小规模集成电路 | 1964 | 1 至 10 | 1 至 12 |

| MSI | 中等规模集成 | 1968 | 10 到 500 | 13 至 99 |

| LSI | 大规模集成化 | 1971 | 500 到 20,0 00 | 100 至 9999 |

| VLSI | 非常大规模的集成 | 1980 | 20 000 至 1 000 000 | 10 000 至 99 999 |

| ULSI | 超级大规模集成 | 1984 | 1 000 000 及以上 | 10 万及以上 |

9.1 SSI、MSI 和 LSI

第一个集成电路只包含几个晶体管。早期包含数十个晶体管的数字电路提供了几个逻辑门,早期的线性集成电路如普莱西 SL201 或飞利浦 TAA320 只有两个晶体管。从那时起,集成电路中晶体管的数量急剧增加。术语 “大规模集成电路”(LSI)首次由 IBM 科学家罗尔夫·兰道尔在描述理论概念时使用;[57]这个术语产生了 “小规模集成”、“中等规模集成”、“超大规模集成” 和 “特大规模集成” 等术语。早期的集成电路是 SSI。

SSI 电路对早期的航空航天项目至关重要,航空航天项目有助于激励技术的发展。民兵导弹和阿波罗计划都需要重量轻的数字计算机作为惯性制导系统。虽然阿波罗制导计算机领导并推动了集成电路技术,[58]但却是民兵导弹迫使它大规模生产。民兵导弹计划和各种其他美国海军计划在 1962 年占集成电路市场总额的 400 万美元,到 1968 年,美国政府在太空和国防上的支出仍然占 3.12 亿美元总产量的 37

美国政府的需求支持了新生的集成电路市场,直到成本下降到足以让集成电路公司进入工业市场,并最终进入消费者市场。每个集成电路的平均价格从 1962 年的 50 美元下降到 1968 年的 2.33 美元。[59]在 20 世纪 70 年代初,集成电路开始出现在消费品行业中。一个典型的应用是调频电视接收机中的载波间声音处理。

第一批 MOS 芯片是 NASA 的小规模集成芯片 卫星[60]

集成电路发展的下一步是在 20 世纪 60 年代末,引入了每个芯片上包含数百个晶体管的器件,称为 “中等规模集成”(MSI)。

在 1964 年,弗兰克·万拉斯演示了一个 16 位单芯片移位寄存器,他在当时难以置信地将 120 个晶体管集成在一个芯片上。[60][61]

MSI 设备在经济上很有吸引力,因为虽然它们的生产成本比 SSI 设备高一点,但它们允许使用更小的电路板来生产更复杂的系统,由于更少的独立组件,组装工作更少,以及许多其他优势。

在相同经济因素的驱动下,进一步的发展导致了 20 世纪 70 年代中期的 “大规模集成电路”,每个芯片上有数万个晶体管。

用于处理和制造 SSI、MSI 和早期 LSI 和 VLSI 器件(如 20 世纪 70 年代早期的微处理器)的掩模大多是手工制造的,通常使用 Rubylith 胶带或类似材料。[62]对于大型或复杂的集成电路(如存储器或处理器),这通常由专门聘请的负责电路布局的专业人员完成,他们置于一组工程师的监督下,工程师还将与电路设计人员一起检查和验证每个掩模的正确性和完整性。

1K 位的 RAM、计算器芯片和第一批微处理器等集成电路在 20 世纪 70 年代初开始适度生产,晶体管不到 4000 个。真正的大规模集成电路,接近 10,000 个晶体管,大约在 1974 年开始生产,用于计算机主存储器和第二代微处理器。

一些 SSI 和 MSI 芯片,如分立晶体管,仍然是大规模生产的,既用于维护旧设备,也用于构建只需要几个栅极的新器件。例如,TTL 芯片的 7400 系列已经成为事实上的标准,并仍在生产中。

9.2 超大规模集成电路

从 20 世纪 80 年代开始,一直持续到现在,发展过程的最后一步是 “超大规模集成”(VLSI )。这种发展始于 20 世纪 80 年代早期的几十万个晶体管,截至 2016 年晶体管数量继续增长,每芯片超过 100 亿个晶体管。

为了实现这种密度的增加,需要很多方面的发展。制造商转向更小的设计规则和更洁净的工艺室,这样他们可以制造更多晶体管的芯片,并保持足够的产量。过程改进的路径由国际半导体技术发展蓝图(ITRS)所总结,后来被设备和系统的国际路线图(IRDS)接手。EDA 改进到足以在合理的时间内完成这些设计。更高能效的 CMOS 取代了 NMOS 和 MOS 管,避免了功耗过高的上升。现代超大规模集成电路器件包含如此多的晶体管、层,互相连络和其他功能,即不再可行的检查掩膜或原始的手工设计。相反,工程师使用 EDA 执行大多数功能验证工作的工具。[63]

1986 年,第一个一兆位随机存取存储器引入了包含一百万多个晶体管的芯片。微处理器芯片在 1989 年突破百万晶体管大关,在 2005 年突破十亿晶体管大关。[64]这一趋势基本上没有减弱,2007 年推出的芯片包含数百亿个存储晶体管。[65]

9.3 ULSI、WSI、SoC 和 3D-IC

为了反映复杂性的进一步增长,术语 ULSI 代表 “超大规模集成”,是为超过 100 万个晶体管的芯片提出的。[66]

晶圆级集成 (WSI)是一种构建非常大的集成电路的方法,它使用整个硅片来生产单个 “超级芯片”。通过大尺寸和减少包装的结合,WSI 可以大幅降低一些系统的成本,特别是大规模并行超级计算机。这个名字取自超大规模集成电路这个术语,它是 WSI 发展时的最新水平。[67]

片上系统 (SoC 或 SoC)是一种集成电路,其中计算机或其他系统所需的所有组件都包含在单个芯片上。这种装置的设计可能复杂且昂贵,并且在一块硅片上构造分立元件可能会损害某些方面的效率。然而,这些缺点被较低的制造和组装成本以及大大降低的功率分配所抵消:因为元件之间的信号保持在管芯上,所以所需的功率要小得多(参见)中。[68]此外,信号源和接收点在芯片上物理上更接近,这减少了布线长度,从而减少了相同芯片上模块之间通信的延迟、传输功率成本和余热。这导致了对所谓的片上网络 (NoC)设备的探索,这些设备将片上系统设计方法应用于数字通信网络,而不是传统的总线架构。

三维集成电路 (3D-IC)具有两层或更多层有源电子元件,它们垂直和水平集成到单个电路中。层间通信使用片内信号,因此功耗比等效的独立电路低得多。明智地使用短的垂直电线可以大大减少总电线长度,从而加快操作速度。[69]

10. 硅标签和涂鸦

为了在生产过程中进行识别,大多数硅片的一个角落都有序列号。添加制造商标识也很常见。自从集成电路诞生以来,一些芯片设计者就使用硅表面区域来制作秘密的、不起作用的图像或文字。这些有时被称为芯片艺术、硅艺术、硅涂鸦或硅涂鸦。

11. 集成电路和集成电路系列

- 555 计时器

- 741 运算放大器

- 7400 系列 TTL 逻辑构建模块

- 4000 系列,对应 7400 系列的 CMOS 版本(另请参见:74HC00 系列)

- 英特尔 4004,世界上第一台微处理器,它引领了著名的 8080 中央处理器,然后是 IBMPC²的 8088,80286,486 等。

- MOS 科技·6502 和 Zilog Z80 微处理器,在 20 世纪 80 年代早期的许多家用计算机中使用

- 摩托罗拉 6800 系列计算机相关芯片,产生了 68000 和 88000 系列(用于一些苹果电脑和 20 世纪 80 年代康茂德 Amiga 系列)

- 模拟集成电路的 LM 系列

12. 参考文献

- "Integrated circuit (IC)". JEDEC..

- Andrew Wylie (2009). "The first monolithic integrated circuits". Retrieved 14 March 2011. Nowadays when people say 'integrated circuit' they usually mean a monolithic IC, where the entire circuit is constructed in a single piece of silicon..

- Horowitz, Paul; Hill, Winfield (1989). The Art of Electronics (2nd ed.). Cambridge University Press. p. 61. ISBN 978-0-521-37095-0. Integrated circuits, which have largely replaced circuits constructed from discrete transistors, are themselves merely arrays of transistors and other components built from a single chip of semiconductor material..

- "Who Invented the IC? - @CHM Blog - Computer History Museum". www.computerhistory.org..

- "Integrated circuits help Invention". Integratedcircuithelp.com. Retrieved 2012-08-13..

- DE 833366W. Jacobi/SIEMENS AG: "Halbleiterverstärker" priority filing on 14 April 1949, published on 15 May 1952..

- 《杰弗里·杜默的不幸故事》 Archived 11 5 月 2013 at the Wayback Machine,(未注明),(超文本标记语言),电子产品新闻,2008 年 7 月 8 日查阅。.

- Rostky, George. "Micromodules: the ultimate package". EE Times. Archived from the original on 2010-01-07. Retrieved 2018-04-23..

- "The RCA Micromodule". Vintage Computer Chip Collectibles, Memorabilia & Jewelry (in 英语). Retrieved 2018-04-23..

- Dummer, G.W.A.; Robertson, J. Mackenzie (2014-05-16). American Microelectronics Data Annual 1964–65 (in 英语). Elsevier. pp. 392–397, 405–406. ISBN 978-1-4831-8549-1..

- 杰克制造的芯片,(c. 2008),(HTML),德州仪器,检索于 2008 年 5 月 29 日。.

- 杰克·基尔比,小型化电子电路,美国专利局,美国专利 3,138,743,1959 年 2 月 6 日提交,1964 年 6 月 23 日发布。.

- Winston, Brian (1998). Media Technology and Society: A History: From the Telegraph to the Internet. Routledge. p. 221. ISBN 978-0-415-14230-4..

- "Texas Instruments – 1961 First IC-based computer". Ti.com. Retrieved 2012-08-13..

- 诺贝尔网络奖(2000 年 10 月 10 日),2000 年诺贝尔物理学奖,2008 年 5 月 29 日检索.

- "Milestones:First Semiconductor Integrated Circuit (IC), 1958". IEEE Global History Network. IEEE. Retrieved 3 August 2011..

- Kurt Lehovec 的隔离 p-n 专利 交叉点:美国专利 3,029,3661962 年 4 月 10 日批准,1959 年 4 月 22 日提交。罗伯特·诺伊斯在他的文章 “微电子学” 中称赞了莱霍韦克,科学美国人,1977 年 9 月,第 23 卷,第 3 号,第 63-69 页。.

- 费德里科·费金,第一个微处理器的制造,IEEE 固态电路杂志,2009 年冬季,IEEE Xplore.

- Davari, Bijan, Robert H. Dennard, and Ghavam G. Shahidi (1995). "CMOS scaling for high performance and low power-the next ten years" (PDF). Proceedings of the IEEE. 83 (4). pp. 595–606.CS1 maint: Multiple names: authors list (link).

- "Qualcomm and Samsung Collaborate on 10nm Process Technology for the Latest Snapdragon 835 Mobile Processor". news.samsung.com (in 英语). Retrieved 2017-02-11..

- "International Roadmap for Devices and Systems" (PDF). IEEE. 2016..

- H. Fujita (1997). A decade of MEMS and its future. Tenth Annual International Workshop on Micro Electro Mechanical Systems..

- A. Narasimha; et al. (2008). "A 40-Gb/s QSFP optoelectronic transceiver in a 0.13 µm CMOS silicon-on-insulator technology". Proceedings of the Optical Fiber Communication Conference (OFC): OMK7..

- M. Birkholz; A. Mai; C. Wenger; C. Meliani; R. Scholz (2016). "Technology modules from micro- and nano-electronics for the life sciences". WIREs Nanomed. Nanobiotech. 8 (3): 355–377. doi:10.1002/wnan.1367. PMID 26391194..

- A.H.D. Graham; J. Robbins; C.R. Bowen; J. Taylor (2011). "Commercialisation of CMOS Integrated Circuit Technology in Multi-Electrode Arrays for Neuroscience and Cell-Based Biosensors". Sensors. 11 (5): 4943–4971. doi:10.3390/s110504943. PMC 3231360. PMID 22163884..

- Zvi Or-Bach。“为什么 SOI 是半导体的未来技术>”。2013..

- >三星的八层闪存出现在苹果的 iPhone 4 中 “”。2010..

- “球形半导体射电温度传感器”。NatureInterface.2002 ..

- Takeda, Nobuo, MEMS applications of Ball Semiconductor Technology (PDF), archived from the original (PDF) on 2015-01-01.

- 维基百科(2018)小芯片引用 IEDM 2017,苏姿丰博士访问日期=2019-05-26.

- 汤姆·西蒙尼特(11.06.18)为了跟上穆尔定律,芯片制造商转向 “小芯片”.

- 克里斯托弗·舒特(04.16.19)升级:今年是中央处理器 “小芯片” 年。.

- Mark LaPedus (16 April 2015). "FinFET Rollout Slower Than Expected". Semiconductor Engineering..

- "About the EDA Industry". Electronic Design Automation Consortium. Archived from the original on 2 August 2015. Retrieved 29 July 2015..

- Paul R. Gray; Paul J. Hurst; Stephen H. Lewis; Robert G. Meyer (2009). Analysis and Design of Analog Integrated Circuits. Wiley. ISBN 978-0-470-24599-6..

- Jan M. Rabaey; Anantha Chandrakasan; Borivoje Nikolic (2003). Digital Integrated Circuits (2nd Edition). Pearson. ISBN 978-0-13-090996-1..

- Jacob Baker (2008). CMOS: Mixed-Signal Circuit Design. Wiley. ISBN 978-0-470-29026-2..

- "CD4068 data sheet" (PDF). Intersil..

- "Inside Pascal: NVIDIA's Newest Computing Platform". 2016-04-05.。610 毫米的 15,300,000,000 个晶体管 2。.

- Nathawad, L.; Zargari, M.; Samavati, H.; Mehta, S.; Kheirkhaki, A.; Chen, P.; Gong, K.; Vakili-Amini, B.; Hwang, J.; Chen, M.; Terrovitis, M.; Kaczynski, B.; Limotyrakis, S.; Mack, M.; Gan, H.; Lee, M.; Abdollahi-Alibeik, B.; Baytekin, B.; Onodera, K.; Mendis, S.; Chang, A.; Jen, S.; Su, D.; Wooley, B. "20.2: A Dual-band CMOS MIMO Radio SoC for IEEE 802.11n Wireless LAN" (PDF). IEEE Entity Web Hosting. IEEE. Retrieved 22 October 2016..

- “热加工超声波焊接-通过修复工艺促进金属流动的方法”,程序。第 20 届 IEEE 电子元件会议。华盛顿哥伦比亚特区,1970 年 5 月,第 549-556 页。].

- Max Chafkin; Ian King (June 9, 2016). "How Intel Makes a Chip". Bloomburg Businessweek..

- Mark Lapedus (May 21, 2015). "10 nm Fab Watch". Semiconductor Engineering..

- Moammer, Khalid (2016-09-16). "AMD Zen CPU & AM4 Socket Pictured, Launching February 2017 – PGA Design With 1331 Pins Confirmed". Wccftech (in 英语). Retrieved 2018-05-20..

- "Ryzen 5 2500U – AMD – WikiChip" (in 英语). Retrieved 2018-05-20..

- "AMD's 'TR4' Threadripper CPU socket is gigantic". PCWorld (in 英语). Retrieved 2018-05-20..

- "Federal Statutory Protection for Mask Works" (PDF). United States Copyright Office. United States Copyright Office. Retrieved 22 October 2016..

- "Washington Treaty on Intellectual Property in Respect of Integrated Circuits". w 彼得·克拉克 ww.wipo.int..

- 1995 年 1 月 1 日与贸易有关的知识产权协定《与贸易有关的知识产权协定》(世界贸易组织(世贸组织)协定附件 1C)生效。《与贸易有关的知识产权协议》第二部分第 6 节保护半导体芯片产品,是 1995 年 3 月 23 日总统公告第 6780 号的基础,该公告根据《斯德哥尔摩公约》第 902(a)(2)条,将保护范围扩大到世贸组织所有现有和未来成员。.

- 日本是第一个颁布自己版本的 SCPA(1985 年日本《半导体集成电路电路布局法》)的国家。.

- 1986 年,欧共体颁布了一项指令,要求其成员通过保护半导体地形的国家立法。1986 年 12 月 16 日关于半导体产品形貌的法律保护,第 1(1)(b)条,1987 年《刑事诉讼法》(第 24 条)第 36 条。.

- "-". ieeexplore.ieee.org..

- "芯片革命给程序员带来问题”,《新科学家》(第 193 卷,第 2594 号).

- 彼得·克拉克,英特尔进入十亿晶体管处理器时代,《EE 时报》,2005 年 10 月 14 日.

- https://web.archive.org/web/20221028221758/http://www . iutbayonne . univ-pau . fr/~ dalmau/documents/cours/archi/micro ancien . pdf.

- Bulletin de la Societe fribourgeoise des sciences naturelles, Volumes 62 à 63 (in 法语). 1973..

- Safir, Ruben (March 2015). "System On Chip - Integrated Circuits". NYLXS Journal. ISBN 9781312995512..

- Mindell, David A. (2008). Digital Apollo: Human and Machine in Spaceflight. The MIT Press. ISBN 978-0-262-13497-2..

- Ginzberg, Eli (1976). Economic impact of large public programs: the NASA Experience. Olympus Publishing Company. p. 57. ISBN 978-0-913420-68-3..

- Bob Johnstone (1999). We were burning: Japanese entrepreneurs and the forging of the electronic age. Basic Books. pp. 47–48. ISBN 978-0-465-09118-8..

- Lee Boysel (2007-10-12). "Making Your First Million (and other tips for aspiring entrepreneurs)". U. Mich. EECS Presentation / ECE Recordings..

- "Intel's Accidental Revolution". CNET..

- 安东内尔。“使用大规模集成的系统工程”。第 870 页。.

- 彼得·克拉克,EE 时报:英特尔进入十亿晶体管处理器时代 2005 年 11 月 14 日.

- 安东尼·贡萨尔维斯,EE 时报 “三星开始生产 16gb 闪存”,2007 年 4 月 30 日.

- Meindl, J.D. (1984). "Ultra-large scale integration". IEEE Transactions on Electron Devices. 31 (11): 1555–1561. doi:10.1109/T-ED.1984.21752. Retrieved 21 September 2014..

- Shanefield, Daniel. "Wafer scale integration". google.com/patents. Retrieved 21 September 2014..

- Klaas, Jeff. "System-on-a-chip". google.com/patents. Retrieved 21 September 2014..

- Topol, A.W.; Tulipe, D.C.La; Shi, L; et., al (2006). "Three-dimensional integrated circuits". IBM Journal of Research and Development. 50 (4.5): 491–506. doi:10.1147/rd.504.0491..